# Software Synthesis for System on Chip

Haobo Yu

Ph.D. Final Defense Information and Computer Science

Committee Members: Professor Daniel D. Gajski Professor Rainer Doemer Professor Tony Givargis

Ph.D. Final Defense

copyright©2004 Haobo Yu

## **Outline**

- Introduction

- Related work

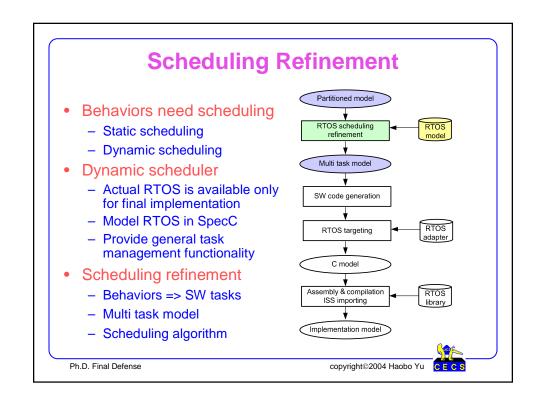

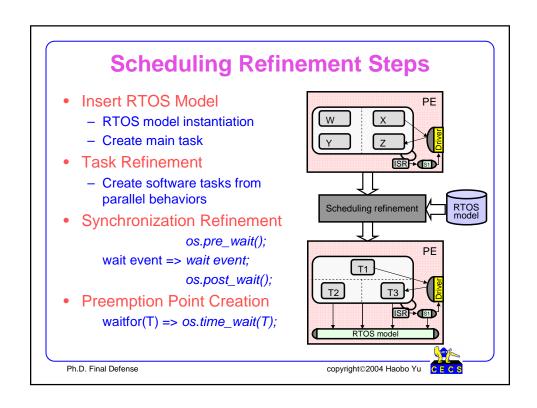

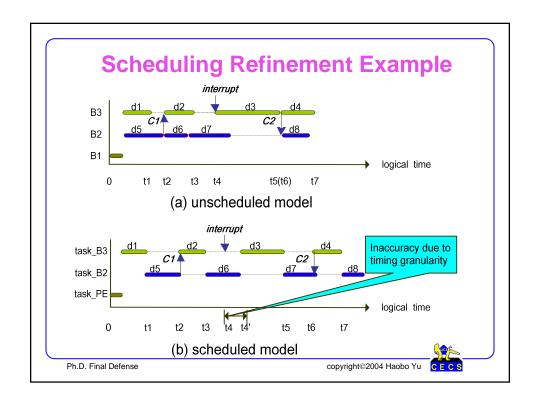

- RTOS scheduling refinement

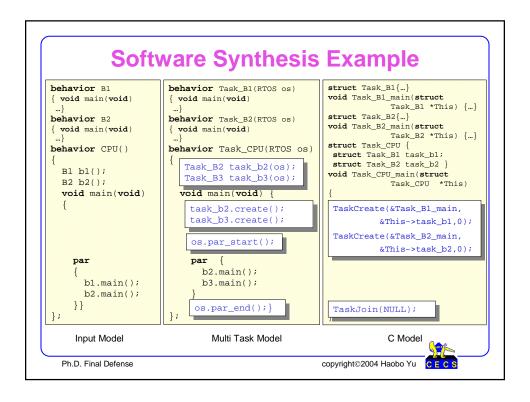

- Code generation

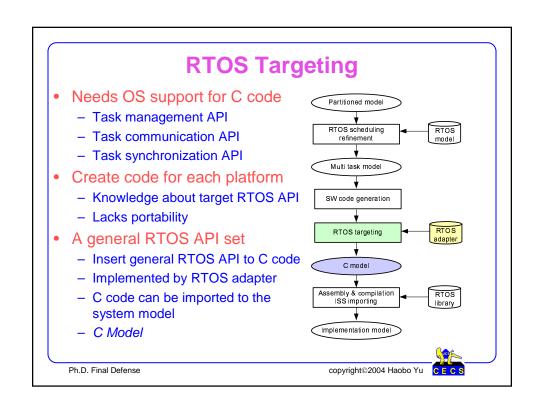

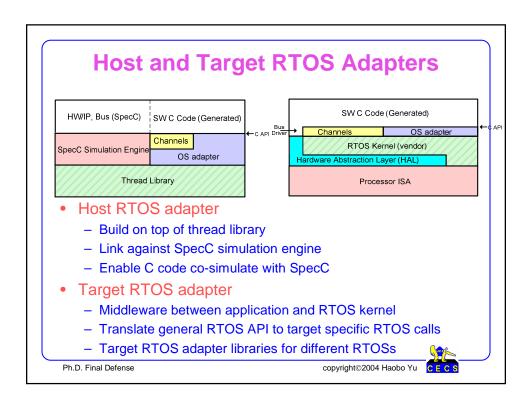

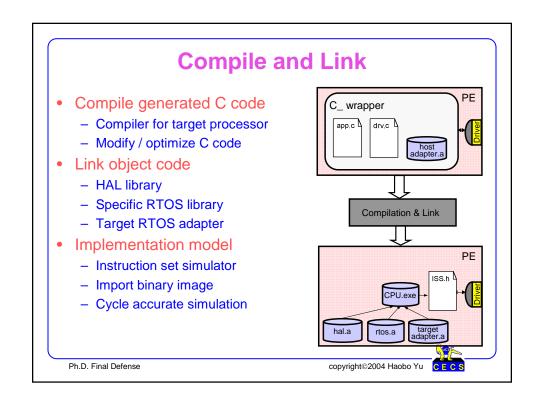

- RTOS targeting

- · Experimental results

- Conclusions

Ph.D. Final Defense

copyright©2004 Haobo Yu

#### Introduction

- System level design

- System level description languages (SpecC, SystemC)

- High level system models for exploration and synthesis

- Increasing significance of embedded SW in SoC

- Embedded processors are widely used in SoC design

- Typical SoC contains processor, HW and communication arch.

- Complex SW is needed to drive the system

- 50-70% of SoC design process is used for SW development (source: Virtual Socket Interface Alliance)

- New method for creating embedded software for SoC

Ph.D. Final Defense

copyright©2004 Haobo Yu

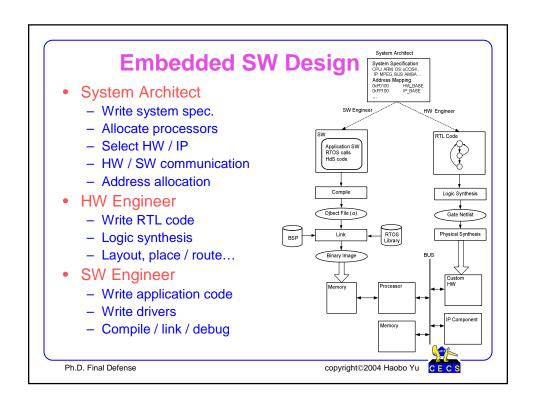

## **Embedded Software for SoC**

- Concepts

- Application software

- Real time operating system (RTOS)

- Hardware dependent software (HdS)

- Development Tool

- Processor IP vender (ARM:ADS)

- RTOS venders (WindRiver:Tornado,GreenHill: MULTI)

- FPGA tool (Altera:SOPC Builder, Xilinx:EDK)

- DSP tool (MathWorks:MATLAB, Cadence:SPW)

Ph.D. Final Defense

copyright@2004 Haobo Yu

#### Related work

- RTOS Modeling

- Specific target implementations [Tomiyama01]

- Proprietary language & simulation engine [Desmet00]

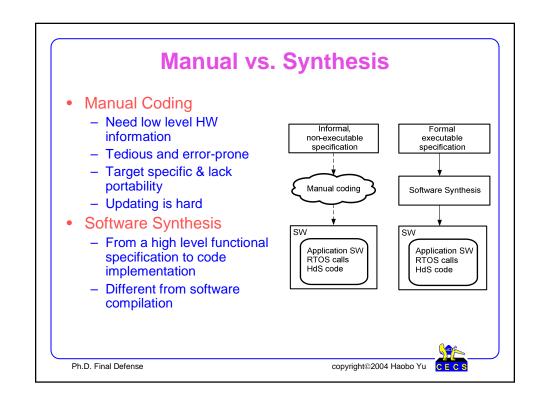

- Software Synthesis and Code Generation

- From abstract model (UML) [Rational]

- From graphical finite state machine (StateCharts) [Harel90]

- From synchronous programming languages (Esterel) [Boussinot91]

- Reactive real time systems (POLIS) [Baladrin97]

- Software scheduling [Cortadella00]

- OS generation and application targeting [Gauthier01]

- Redefinition and overloading of SystemC class [Herrera03]

- Substituting SystemC modules with C structures [Groetker03]

Ph.D. Final Defense

copyright@2004 Haobo Yu CECS

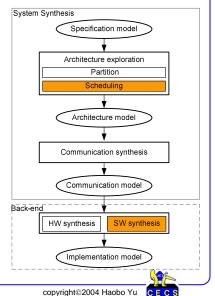

## SW Synthesis in System Level Design

- Architecture exploration

- Schedule SW behaviors

- Create SW tasks

- Evaluate different scheduling algorithms

- Back-end

- Generate C code

- Generate bus drivers

- Target for RTOS

- Compile & Link

Ph.D. Final Defense

# **Experiment**

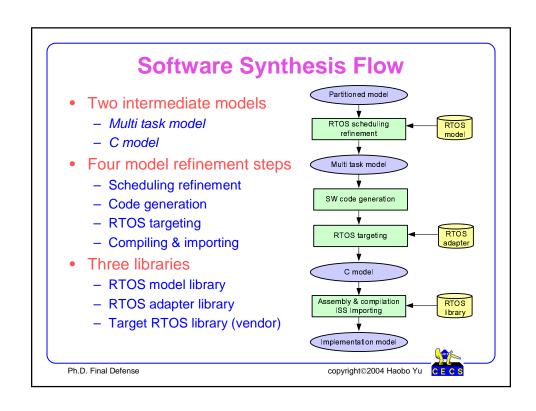

- Developed software synthesis tools for SpecC

- Scheduling refinement tool scos

- Code generation tool sc2c

- Integrated in SoC Design Environment (SCE) toolset

- Examples

- GSM Vocoder

- JPEG encoder

- Motor controller

- Mp3 decoder

- Inter-task communication examples

CECS

Ph.D. Final Defense

copyright@2004 Haobo Yu

## **SW Code Generation Results**

| Design  |       | Behaviors | Channels | SW<br>Tasks | C Code<br>(#LoC) | Code<br>Gen. | Manual<br>Coding |

|---------|-------|-----------|----------|-------------|------------------|--------------|------------------|

| Vocoder | SW    | 109       | 0        | 1           | 9,805            | 1.41s        | 98h              |

|         | HW/SW | 107       | 1        | 2           | 9,244            | 1.57s        | 92h              |

| Мр3     | SW    | 131       | 3        | 16          | 33,519           | 5.98s        | 335h             |

|         | HW/SW | 147       | 7        | 34          | 32,092           | 9.24s        | 320h             |

| JPEG    | SW    | 36        | 0        | 1           | 1,655            | 0.21s        | 16h              |

|         | HW/SW | 29        | 6        | 2           | 1,959            | 0.31s        | 19h              |

| Motor   | SW    | 29        | 3        | 9           | 2,245            | 0.28s        | 22h              |

|         | HW/SW | 25        | 8        | 5           | 2,300            | 0.32s        | 23h              |

- Generate SW for different system arch. in seconds

- 1000x productivity gain

Ph.D. Final Defense

#### Implement GSM voice encoder on FPGA Xilinx Virtex-II FPGA - Processor: Microblaze - RTOS: uC/OS-II - Bus: OPB Bus On-chip GSM Vocoder SW **GSM Vocoder HW** Block RAM DLMB ILMB Other OPB Interrupt MicroBlaze MicroBlaze Controller OPB (On-chip Peripheral Bus) IOPB DOPB Off-chip Off-chip Timer JTAG Memory Memory Ph.D. Final Defense copyright@2004 Haobo Yu

### **Conclusions**

- Benefits of software synthesis

- Relieves designers from the tedious, error-prone code writing process

- Eliminates the need to maintain two versions of software

- · Contributions of my dissertation

- Software synthesis flow with well defined design steps

- Demonstrated effectiveness and productivity gain through experiment

- C and SpecC co-simulation enables validation of C code through fast C model simulation instead of using instruction set simulation

- C model serves as a virtual system prototype for designers to add/debug/validate new application software to the system

- Defined a way to model RTOSs in SpecC, which enables scheduling exploration in the early stages of system design

- Future work

- Apply software synthesis to models in SystemC

- Introduce more features for RTOS models in SpecC

Ph.D. Final Defense

copyright©2004 Haobo Yu

Ph.D. Final Defense

copyright©2004 Haobo Yu CECS