# EECS 222A: System-on-Chip Description and Modeling Lecture 1

#### Rainer Dömer

doemer@uci.edu

The Henry Samueli School of Engineering Electrical Engineering and Computer Science University of California, Irvine

#### Lecture 1: Overview

- Course administration

- Overview

- Contents

- Schedule

- Assignments

- Introduction to System-on-Chip design

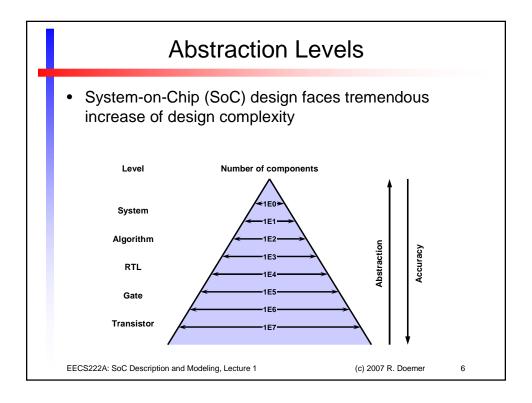

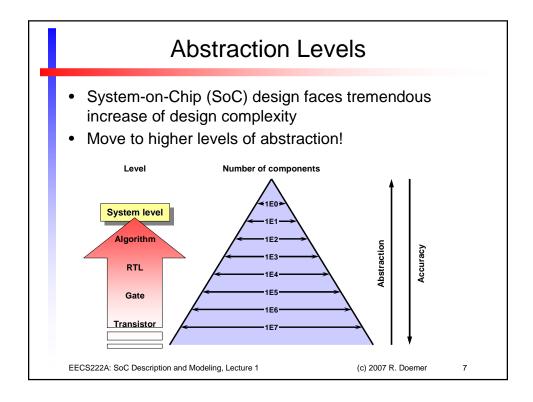

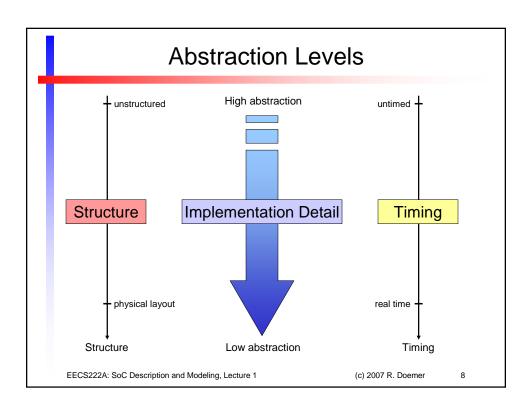

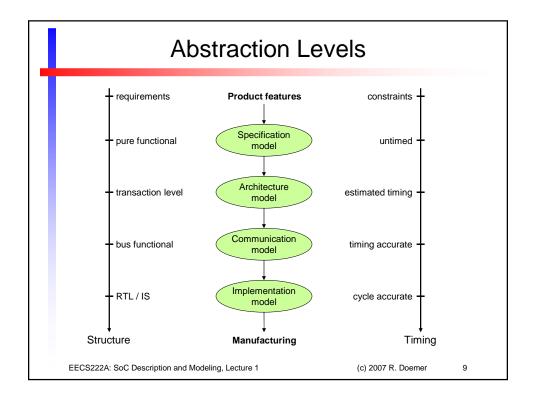

- Levels of abstraction

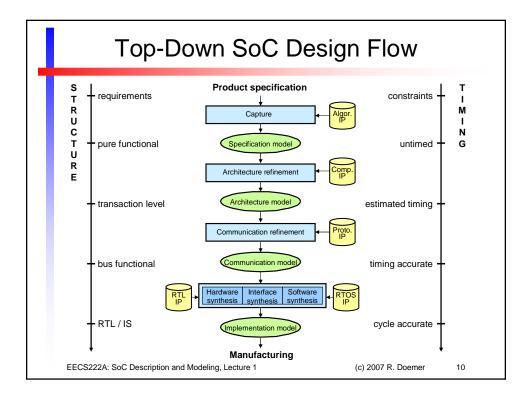

- System design flow

- Computational models

- System-level description languages

- Computation, communication, IP

EECS222A: SoC Description and Modeling, Lecture 1

(c) 2007 R. Doemer

2

#### Course Administration

- Course web pages at http://eee.uci.edu/07f/18430/

- Instructor information

- Course description and policies

- Objectives and outcomes

- Contents and schedule

- Resources and communication

- Assignments

EECS222A: SoC Description and Modeling, Lecture 1

(c) 2007 R. Doemer

3

### Introduction to SoC Design

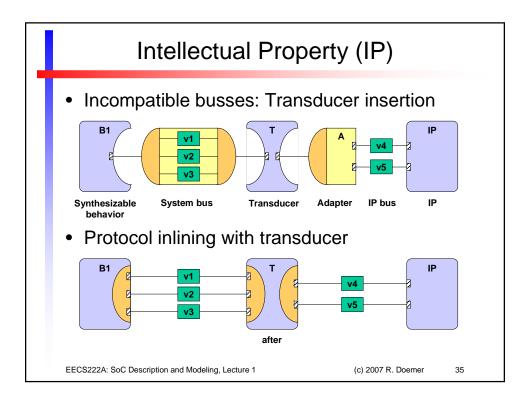

- System-on-Chip (SoC) design

- Abstraction levels

- · SoC design flow

- Computational models

- System-level description languages

- Computation vs. communication

- Intellectual Property (IP)

EECS222A: SoC Description and Modeling, Lecture 1

(c) 2007 R. Doemer

1

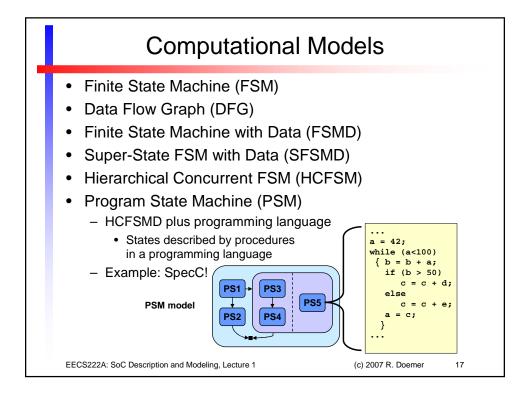

# **Computational Models**

- Models of Computation

- Formal, abstract description of a system

- Various degrees of

- · supported features

- · complexity

- · expressive power

- Examples

- Evolution process from FSM to PSM

- Finite State Machine (FSM)

- FSM with Data (FSMD)

- Super-state FSMD

- ..

- Program State Machine (PSM)

EECS222A: SoC Description and Modeling, Lecture 1

(c) 2007 R. Doemer

11

### **Computational Models**

- Finite State Machine (FSM)

- Basic model for describing control

- States and state transitions

- FSM = <S, I, O, f, h>

- Two types:

- Mealy-type FSM (input-based)

- Moore-type FSM (state-based)

FSM model

EECS222A: SoC Description and Modeling, Lecture 1

(c) 2007 R. Doemer

12

## **Computational Models**

- Finite State Machine (FSM)

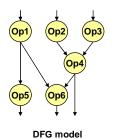

- Data Flow Graph (DFG)

- Basic model for describing computation

- Directed graph

- · Nodes: operations

- · Arcs: dependency of operations

EECS222A: SoC Description and Modeling, Lecture 1

(c) 2007 R. Doemer

13

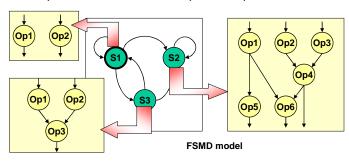

## **Computational Models**

- Finite State Machine (FSM)

- Data Flow Graph (DFG)

- Finite State Machine with Data (FSMD)

- Combined model for control and computation

- FSMD = FSM + DFG

- Implementation: controller plus datapath

EECS222A: SoC Description and Modeling, Lecture 1

(c) 2007 R. Doemer

14

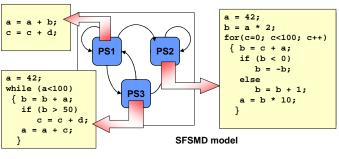

### **Computational Models**

- Finite State Machine (FSM)

- · Data Flow Graph (DFG)

- Finite State Machine with Data (FSMD)

- Super-State FSM with Data (SFSMD)

- FSMD with complex, multi-cycle states

- States described by procedures in a programming language

EECS222A: SoC Description and Modeling, Lecture 1

(c) 2007 R. Doemer

15

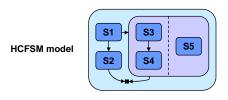

#### **Computational Models**

- Finite State Machine (FSM)

- Data Flow Graph (DFG)

- Finite State Machine with Data (FSMD)

- Super-State FSM with Data (SFSMD)

- Hierarchical Concurrent FSM (HCFSM)

- FSM extended with hierarchy and concurrency

- Multiple FSMs composed hierarchically and in parallel

- Example: Statecharts

EECS222A: SoC Description and Modeling, Lecture 1

(c) 2007 R. Doemer

16

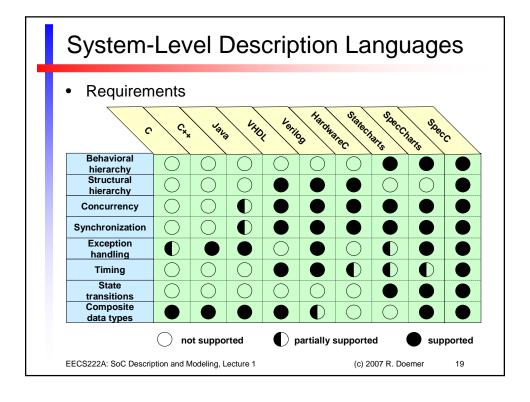

#### System-Level Description Languages

- Goals

- Executability

- Validation through simulation

- Synthesizability

- Implementation in HW and/or SW

- · Support for IP reuse

- Modularity

- · Hierarchical composition

- · Separation of concepts

- Completeness

- · Support for all concepts found in embedded systems

- Orthogonality

- · Orthogonal constructs for orthogonal concepts

- Minimality

- Simplicity

EECS222A: SoC Description and Modeling, Lecture 1

(c) 2007 R. Doemer

18

#### System-Level Description Languages Examples in use today C/C++ · ANSI standard programming languages, software design · traditionally used for system design because of practicality, availability SystemC C++ API and library • initially developed at UCI, supported by Open SystemC Initiative SpecC C extension developed at UCI, supported by SpecC Technology Open Consortium SystemVerilog Verilog with C extensions specification and simulation in engineering, algorithm design UML · unified modeling language, software specification, graphical SDL • telecommunication area, standard by ITU, used in COSMOS · formal specification of requirements, not executable etc. EECS222A: SoC Description and Modeling, Lecture 1 (c) 2007 R. Doemer 20

### System-Level Description Languages

- · Examples in use today

- C/C++

- · ANSI standard programming languages, software design

- · traditionally used for system design because of practicality, availability

- SystemC

- C++ API and library

- initially developed at UCI, supported by Open SystemC Initiative

- SpecC

- C extension

- · developed at UCI, supported by SpecC Technology Open Consortium

- SystemVerilog

- Verilog with C extensions

- Matlab

- · specification and simulation in engineering, algorithm design

- ➤ UMI

- unified modeling language, software specification, graphical

- SDL

- · telecommunication area, standard by ITU, used in COSMOS

- SLDL

- formal specification of requirements, not executable

- etc.

EECS222A: SoC Description and Modeling, Lecture 1

(c) 2007 R. Doemer

21

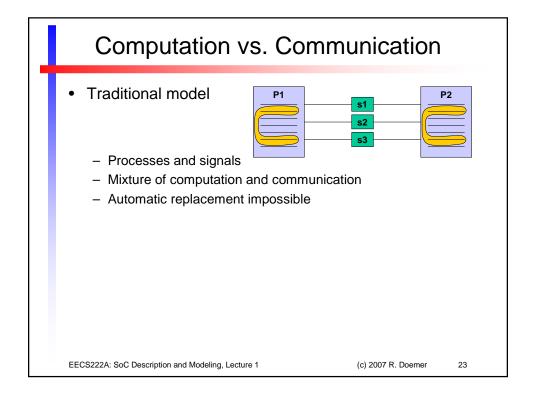

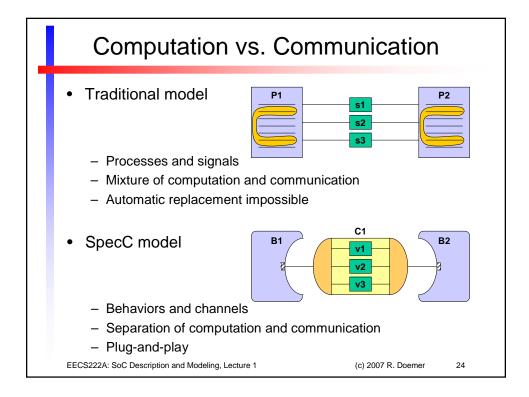

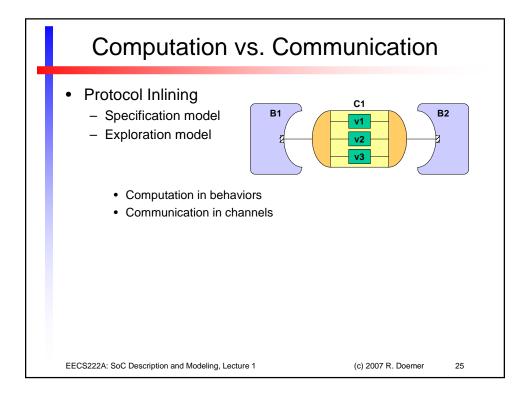

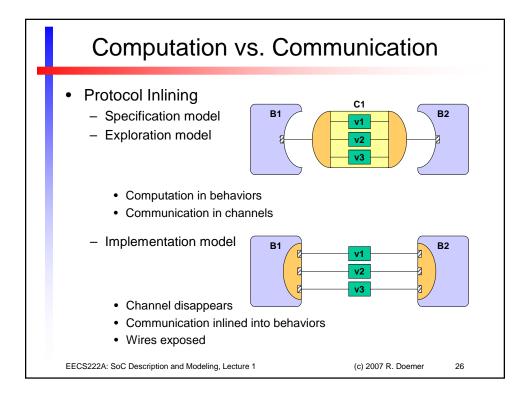

#### Separation of Concerns

- · Fundamental principle in modeling of systems

- Clear separation of concerns

- address separate issues independently

- System-Level Description Language (SLDL)

- orthogonal concepts

- orthogonal constructs

- System-level Modeling

- Computation

- · encapsulated in modules / behaviors

- Communication

- · encapsulated in channels

EECS222A: SoC Description and Modeling, Lecture 1

(c) 2007 R. Doemer

22