## EECS 222: Embedded System Modeling Lecture 13

Rainer Dömer

doemer@uci.edu

The Henry Samueli School of Engineering Electrical Engineering and Computer Science University of California, Irvine

### Lecture 13: Overview

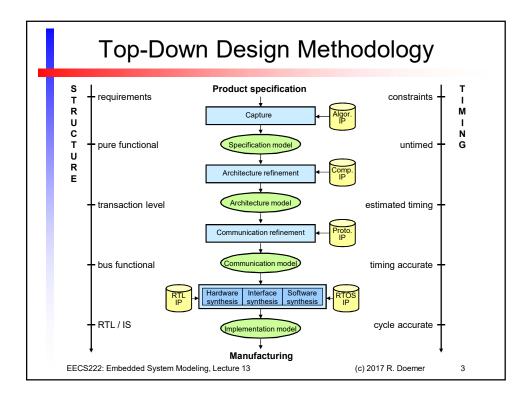

- Embedded System Design Flow

- Top-down design methodology

- Refinement-based design flow

- · Specify

- Explore

- Refine

- System-on-Chip Environment (SCE)

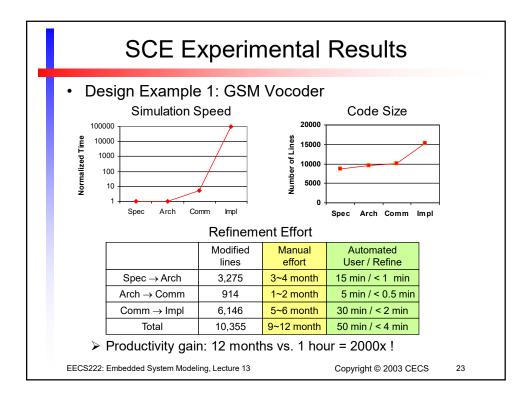

- Design Example: GSM Vocoder

- Interactive Demonstration

EECS222: Embedded System Modeling, Lecture 13

(c) 2017 R. Doemer

2

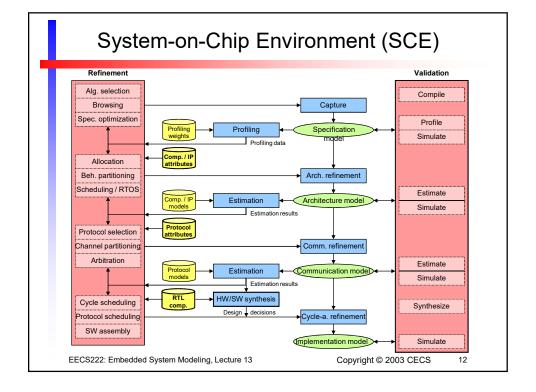

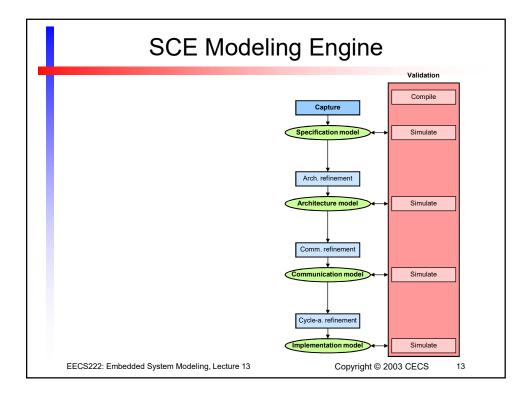

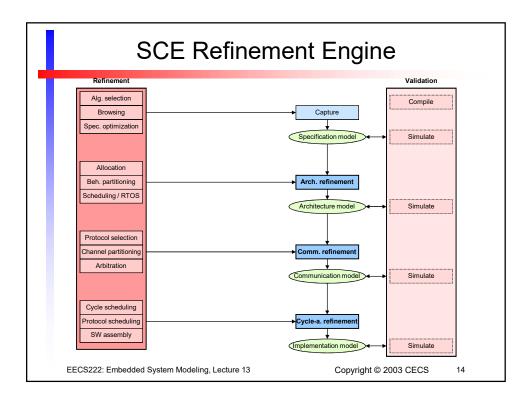

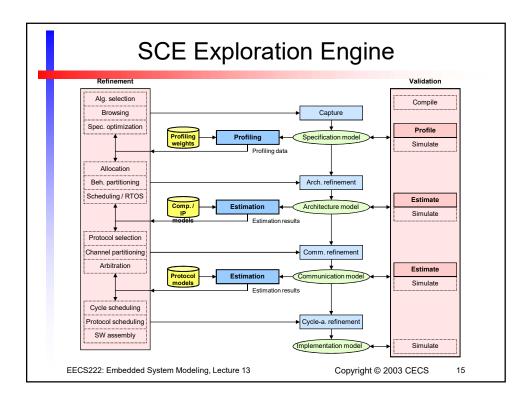

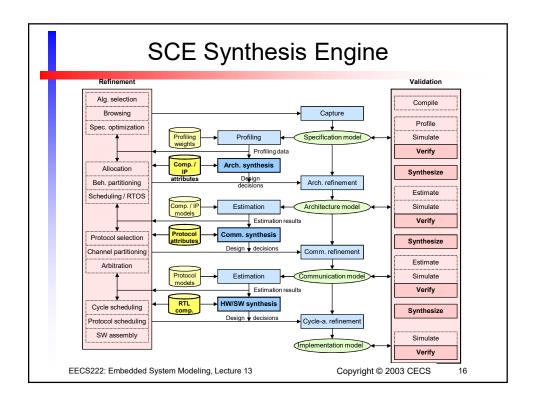

- Refinement steps

- Architecture refinement (Specification -> Architecture)

- Communication refinement (Architecture -> Communication)

- Cycle-accurate refinement (Communication -> RTL/IS)

- · HW / SW / interface synthesis

- Levels of abstraction

- Specification model:

- Architecture model:

- Communication model:

- Implementation model:

- Component data bases

- Algorithms for specification

- Components for architecture

- Busses for communication

- RTOS for SW

- RTL components for HW

EECS222: Embedded System Modeling, Lecture 13

estimated, structural timed, bus-functional cycle-accurate, RTL/IS

untimed, functional

(c) 2017 R. Doemer

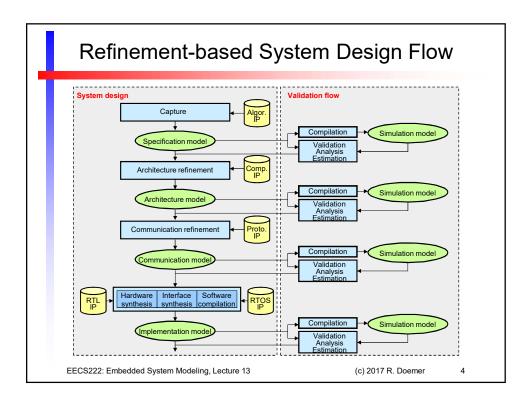

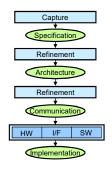

### Refinement-based System Design Flow

- Step 1: Architecture Refinement

- Allocation of Processing Elements (PE)

- · Type and number of processors

- · Type and number of custom hardware blocks

- · Type and number of system memories

- Mapping to PEs

- · Map each behavior to a PE

- · Map each channel to a PE

- Map each variable to a PE

- ➤ Result

- · System architecture of concurrent PEs with abstract communication via channels

EECS222: Embedded System Modeling, Lecture 13

(c) 2017 R. Doemer

### Refinement-based System Design Flow

- Step 2: Scheduling Refinement

- For each PE, serialize the execution of behaviors to a single thread of control

- Option (a): Static scheduling

- For each set of concurrent behaviors, determine fixed order of execution

- Option (b): Dynamic RTOS scheduling

- Choose scheduling policy, e.g. round-robin or priority-based

- For each set of concurrent behaviors, determine scheduling priority

#### > Result

System model with abstract scheduler inserted in each PE

EECS222: Embedded System Modeling, Lecture 13

(c) 2017 R. Doemer

7

### Refinement-based System Design Flow

- Step 3: Network / Communication Refinement

- Allocation of system busses

- Type and number of system busses

- Type of bus protocol for each bus (if applicable)

- Number of transducers (if applicable)

- System connectivity

- Mapping of channels to busses

- Map each channel to a system bus (or a network of multiple busses)

#### > Result

Transaction-Level Model (TLM), or Bus-Functional Model (BFM)

EECS222: Embedded System Modeling, Lecture 13

(c) 2017 R. Doemer

8

(c) 2017 R. Doemer

Δ

### Refinement-based System Design Flow

- Step 4: Hardware Refinement (for HW PE)

- Allocation of Register Transfer Level (RTL) components

- Type and number of functional units (e.g. adder, multiplier, ALU)

- Type and number of storage units (e.g. registers, register files)

- Type and number of interconnecting busses (drivers, multiplexers)

- Scheduling

- · Basic blocks assigned to super-states

- Individual operations assigned to clock cycles

- Binding

- · Bind functional operations to functional units

- · Bind variables to storage units

- · Bind assignments/transfers to busses

- > Result

- · Clock-cycle accurate model of each HW PE

- · Output: Synthesizable Verilog description

EECS222: Embedded System Modeling, Lecture 13

(c) 2017 R. Doemer

9

# Refinement-based System Design Flow

- Step 5: Software Refinement (for SW PE)

- C code generation

- · For selected target processor

- RTOS targeting

- · Thin adapter layer for selected target RTOS

- Cross-compilation to Instruction Set Architecture

- for Instruction Set Simulation (ISS)

- · for target processor embedded in target system

- Assembly and Linking

- > Result

- Clock-cycle accurate, or instruction-accurate model of each SW PE

- · Output: binary image

EECS222: Embedded System Modeling, Lecture 13

(c) 2017 R. Doemer

10

(c) 2017 R. Doemer

5

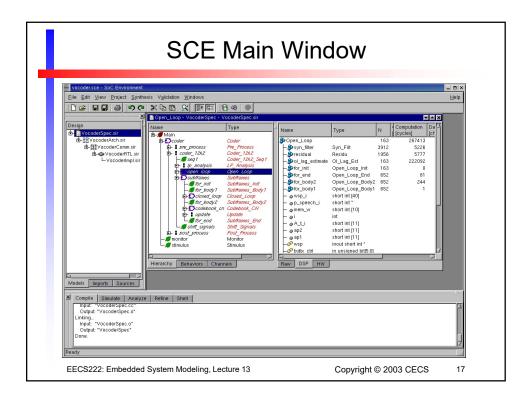

# System-on-Chip Environment (SCE)

- Integrated Development Environment (IDE) with support of:

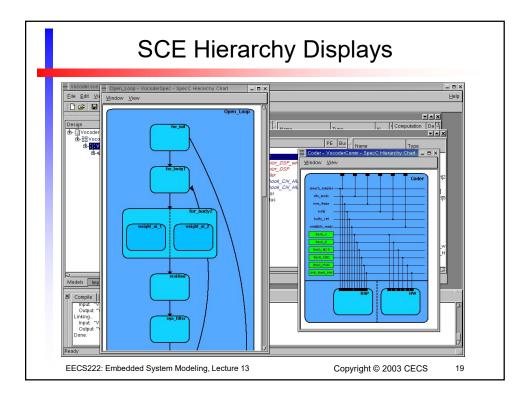

- Graphical frontend (sce, scchart)

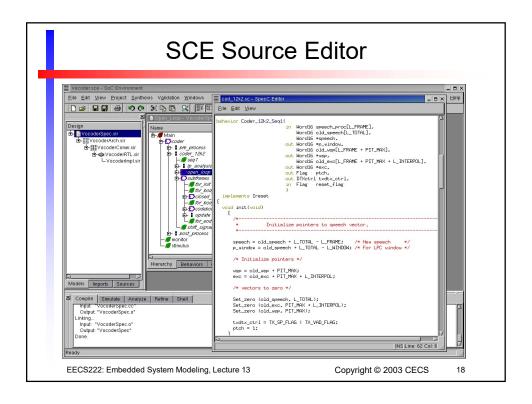

- SLDL-aware editor (sced)

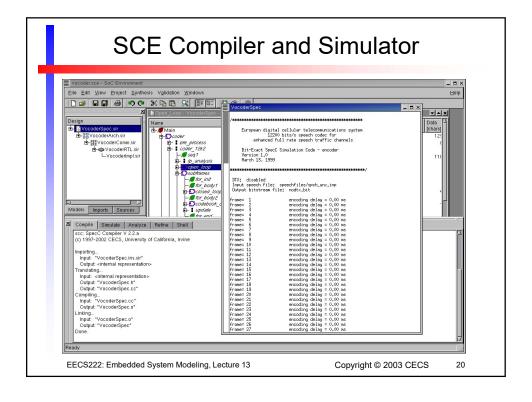

- Compiler and simulator (scc)

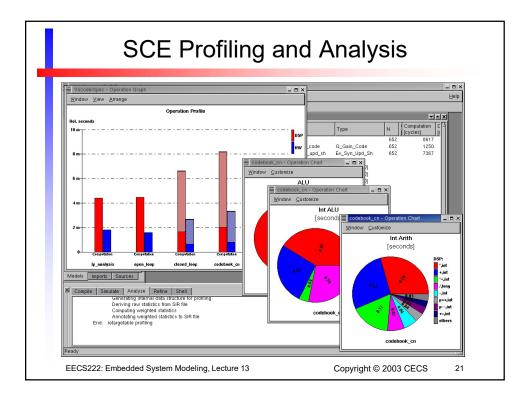

- Profiling and analysis (scprof)

- Architecture refinement (scar)

- RTOS refinement (scos)

- Communication refinement (sccr)

- RTL refinement (scrt1)

- Software refinement (sc2c)

- Scripting interface (scsh)

- Tools and utilities (sir\_list, sir\_tree, ...)

EECS222: Embedded System Modeling, Lecture 13

(c) 2017 R. Doemer

11

### **SCE Demonstration**

- Application Example: GSM Vocoder

- Enhanced full-rate voice codec

- GSM standard for mobile telephony (GSM 06.10)

- · Lossy voice encoding/decoding

- · Incoming speech samples @ 104 kbit/s

- · Encoded bit stream @ 12.2 kbit/s

- Frames of 4 x 40 = 160 samples (4 x 5ms = 20ms of speech)

- Real-time constraint:

- max. 20ms per speech frame (max. total of 3.26s for sample speech file)

- SpecC specification model

- 29 hierarchical behaviors (9 par, 10 seq, 10 fsm)

- 73 leaf behaviors

- 9139 formatted lines of SpecC code (~13000 lines of original C code, including comments)

EECS222: Embedded System Modeling, Lecture 13

Copyright © 2003 CECS

22