# SystemC 2.1 Overview

OSCI Language Working Group February 2004

## Goals of SystemC 2.1

- Improve modularity for IP delivery

- As SystemC 2.0.1 was more widely used for transaction-level design IP and verification IP, several practical barriers emerged

- Provide better support for transaction-level design and verification

- Requirements identified for TLM prior to TLM WG

- Requirements identified by Verification WG

- Resolve longstanding ease-of-use issues

- Inconsistency, non-orthogonality, platform support

- Fix bugs

- Of course

## Modularity, IP Delivery Capability

- Structured error reporting mechanism

- Provides consistent messaging from

- The core simulator

- Add-on libraries

- IP modules

- Testbenches

- Can be customized by vendors for integration with co-simulation messaging

- Access to start-up arguments

- sc\_argc() and sc\_argv() give access to argc and argv from outside of sc\_main

- Allows command line control of Design IP and Verification IP

- Allows command line control of add-on libraries

- New callbacks allow IP integration without needing code in sc\_main

- before\_end\_of\_elaboration()

- start\_of\_simulation()

- end\_of\_simulation()

## Transaction-level Design and Verification

#### sc\_export

Provides a modular capability for a module to advertise internal interfaces for access from outside

#### Dynamic process support

- Crucial for development of transaction-level testbenches

- Also important for software modeling

- Thread creation example from 2.0.1 has been enhanced and incorporated into the language

- Kernel automatically allocates and reclaims threads as needed. No "thread pool" required.

- Uses publicly available boost::bind library

### sc\_event\_queue class

- Catch multiple calls to notify() in same delta cycle

- Allows IP and testbenches to reliably catch every notify()

## Resolve Longstanding Ease-of-use Issues

- Support for programs with their own main() function

- Programs with their own main() function can call sc\_main\_main() to perform SystemC processing.

- Mixed concatenation

- Concatenations of sc\_uint, sc\_biguint, sc\_int, sc\_bigint, sc\_signed, sc\_unsigned etc can now be mixed without ugly casting

- Concatenations can produce results greater than 64 bits

- New API for obtaining process kind info: sc\_get\_cur\_process\_kind()

- Object code release tagging

- link-time detection between incompatible object files

- POSIX thread support

- Allows use of memory leak checking tools

- Support for MacOS X

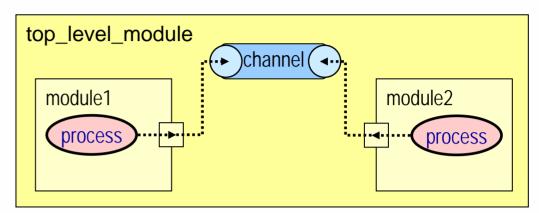

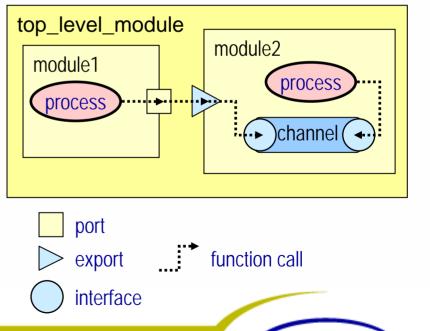

## Importance of sc\_export

- sc\_ports facilitate modular design by precisely declaring interfaces required at a module boundary

- sc\_exports facilitate modular design by precisely declaring interfaces provided at a module boundary

- sc\_ports and sc\_exports allow interfaces to be passed through each level of the hierarchy

- Use of sc\_port and sc\_export improves modularity by avoiding reliance on explicit multilevel paths

- sc\_export permits direct function call interfaces for TLM without introduction of extra process switches

## Technical Details of sc\_export

- SystemC 2.0

- sc\_port indicates sc\_interface is required by an sc\_module

- sc\_interface implemented by channel higher in the hierarchy

- sc\_module calls sc\_interface function through sc\_port

- SystemC 2.1

- sc\_port mechanism exists unchanged

- sc\_export indicates sc\_interface is provided by an sc\_module

- sc\_interface implemented somewhere within the sc\_module

- sc\_port can be bound directly to sc\_export

- Other sc\_module calls sc\_interface function through sc\_port and sc\_export

## **Bug Fixes**

- sc\_start() at max value aborts simulator

- sc\_trace for uint64, int64 missing

- sc\_set\_time\_resolution not properly affecting VCD dump information.

- The value of sc\_clock needs to be updated during update phase, not execution phase.

- sc\_string subscript operator may modify multiple instance because of copy semantics.

- Cpu risc example not shipped anymore

- Error in sc\_bv char constructor

- sc\_biguint partial selection bug

- Missing terminating null char in >> operator for sc\_string.

- The constructor sc\_module(const sc\_module&) is not defined

- Signal initialized in module CTOR not registered with module.

- Deletion of main fiber should not occur in ~sc\_cor\_fiber

- Need ability to compile with Wno-deprecated

- Tracing ports after end\_of\_elaboration had no effect

- wait() in module ctor led to crashes.